AMD si prepara a rivoluzionare le proprie architetture CPU con un’innovazione che potrebbe ridefinire il concetto stesso di processore a chiplet: un nuovo tipo di interconnessione, soprannominato “Sea of Wires”, sarà una delle caratteristiche distintive della futura generazione Zen 6.

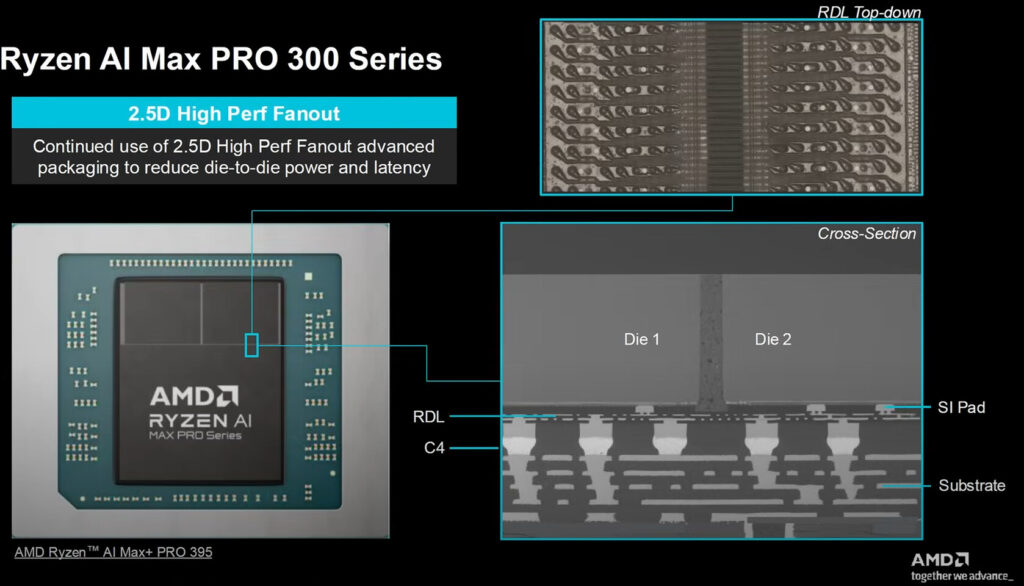

I primi segnali concreti di questo cambiamento si possono già osservare nei nuovi processori Ryzen AI MAX 300 (Strix Halo), testati da High-Yield su un notebook ASUS ROG Flow Z13.

Da SERDES a qualcosa di molto più ambizioso

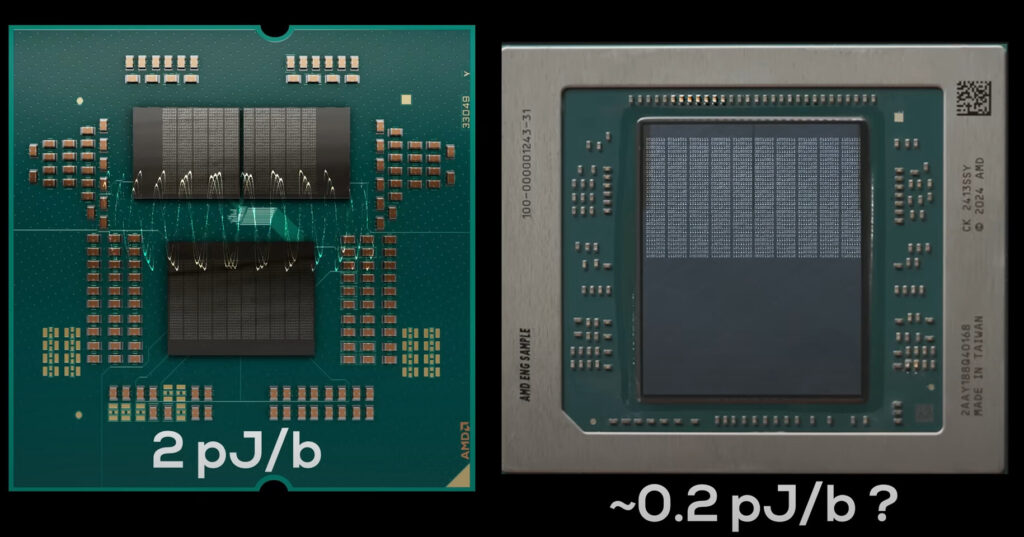

Fino ad oggi, AMD ha utilizzato un’interconnessione di tipo SERDES (Serializer/Deserializer) per connettere i chiplet CPU ai die I/O. Con Zen 6, si passa a una soluzione più avanzata, che richiede l’adozione di tecnologie di packaging più sofisticate. Lo scopo? Far sì che i chiplet AMD si comportino sempre più come un die monolitico, riducendo le latenze interne e migliorando l’efficienza generale del sistema.

Il nuovo design “a mare di fili” consente una connessione a bassa latenza e ad alta ampiezza di banda tra i vari componenti del processore, ridefinendo i limiti delle architetture a chiplet.

Efficienza energetica e prestazioni: i tre vantaggi chiave

Nonostante il nuovo interconnect sia più costoso da produrre, porta con sé tre benefici fondamentali:

Riduzione del consumo energetico:

La trasmissione di dati tra chiplet consuma fino al 90% di energia in meno, secondo le stime di High-Yield. Questo rappresenta un enorme vantaggio soprattutto per i dispositivi mobili e i server, dove l’efficienza energetica è cruciale.Aumento della banda passante:

L’interconnessione aggiornata permette una comunicazione più veloce tra core e I/O die, riducendo i colli di bottiglia legati alla banda disponibile e consentendo ai core CPU di accedere a più memoria con maggiore velocità.Latenze inferiori:

La riduzione della latenza migliora le prestazioni in workload sensibili alla memoria, come giochi, simulazioni e applicazioni scientifiche. Anche le configurazioni multi-CCD (multi-chiplet) ne trarranno vantaggio, con un potenziale aumento della scalabilità e prestazioni multi-thread.

Zen 6: un salto generazionale concreto

Il nuovo sistema di interconnessione non è una semplice teoria: è già presente nei Ryzen AI MAX 300, nome in codice Strix Halo, che rappresentano una sorta di banco di prova per l’innovazione futura. Le ottime prestazioni di questi chip testimoniano il potenziale della nuova architettura di collegamento.

Per Zen 6, AMD estenderà questa tecnologia a una gamma più ampia di processori Ryzen e anche ai nuovi EPYC per il mercato enterprise, portando i benefici del “sea of wires” a un pubblico più vasto. Le indiscrezioni parlavano da tempo di questo cambiamento, ma ora la sua implementazione è una realtà confermata.

Conclusioni: il chiplet non è più un limite

Con l’evoluzione dell’interconnect, AMD sta superando uno dei principali limiti delle architetture a chiplet: la latenza e la banda limitata tra i componenti. Il “Sea of Wires” trasforma ogni chiplet in parte integrante di un ecosistema sempre più simile a un singolo blocco monolitico, senza sacrificare la flessibilità produttiva.

Nel panorama competitivo delle CPU, dove efficienza energetica, scalabilità e latenze sono fondamentali, l’approccio di AMD si dimostra lungimirante. Se le promesse verranno mantenute anche con Zen 6 su larga scala, ci troviamo davanti a una vera rivoluzione per l’architettura x86.

In sintesi

AMD introduce una nuova interconnessione avanzata per CPU chiplet.

Fino al 90% di risparmio energetico nella comunicazione tra die.

Maggiore banda, minori latenze e prestazioni migliorate in Zen 6.

Tecnologia già presente nei Ryzen AI MAX (Strix Halo).

Attesa l’adozione estesa anche nei futuri EPYC.

HW Legend Staff