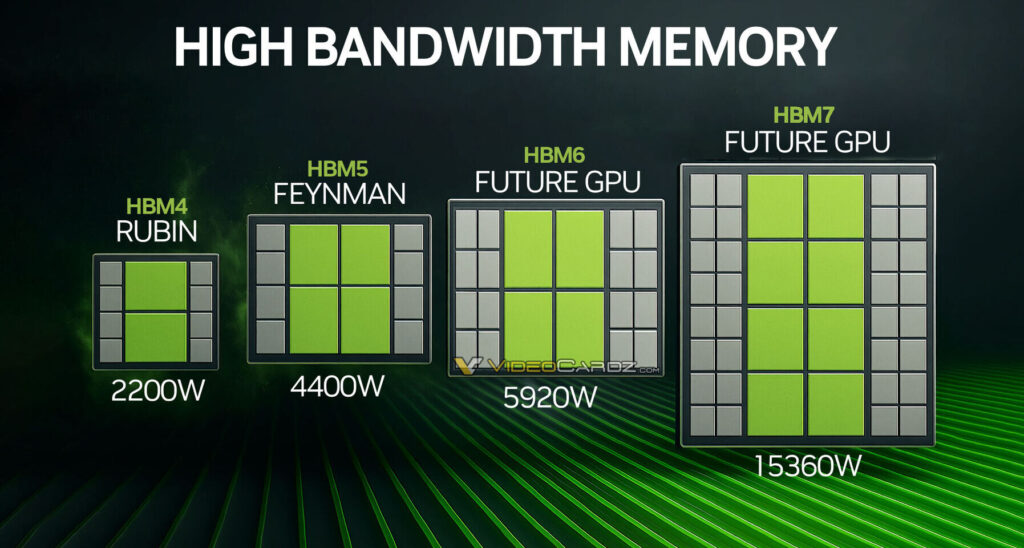

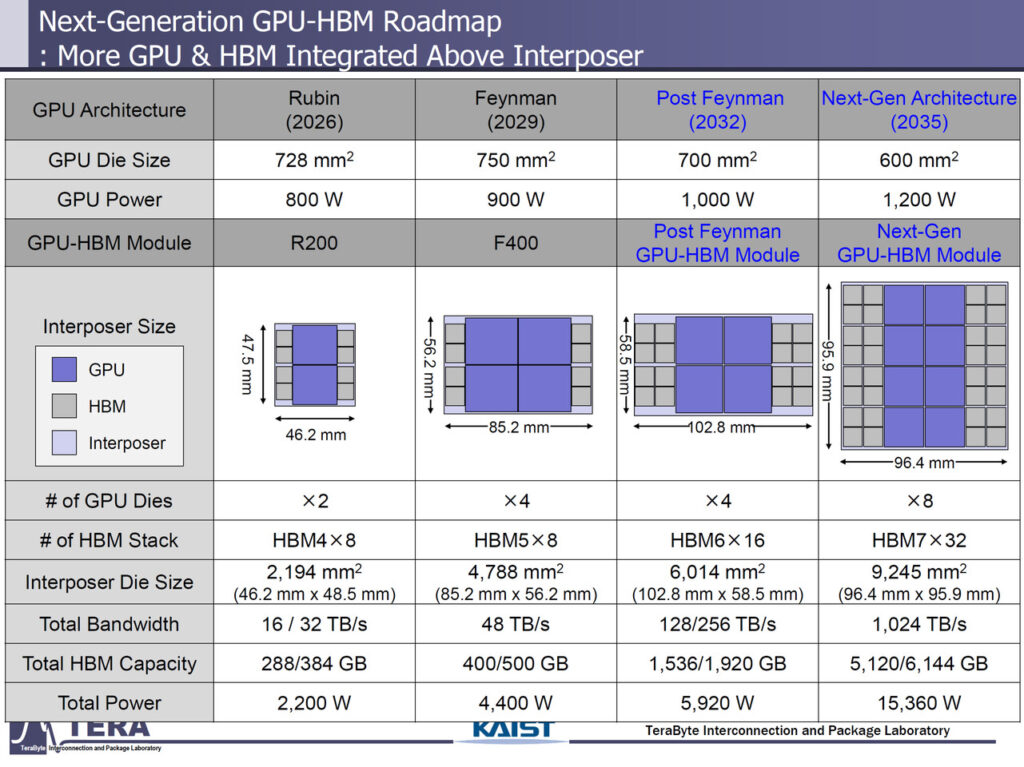

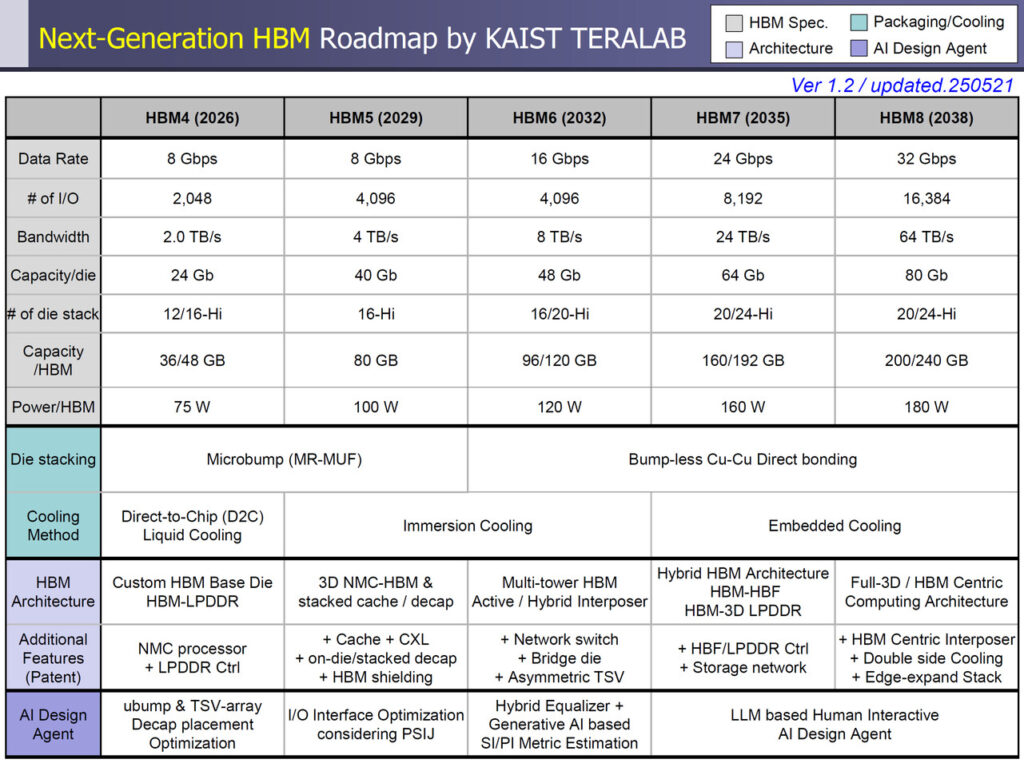

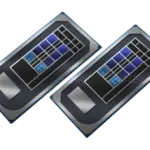

Durante un briefing congiunto tra il Memory Systems Laboratory del KAIST e il gruppo Interconnection and Packaging di TERA, è stata presentata una roadmap ambiziosa e dettagliata per le future generazioni di memoria HBM (High Bandwidth Memory).

Il documento, riportato da Wccftech e VideoCardz, delinea cinque evoluzioni successive del formato HBM, da HBM4 a HBM8, con traguardi impressionanti in termini di capacità, larghezza di banda e ingegneria di packaging.

HBM4 (2026): il primo salto verso 2 TB/s per stack

La prossima generazione, HBM4, è attesa per il 2026 e sarà adottata nei GPU per l’intelligenza artificiale e acceleratori da data center. Le sue specifiche tecniche parlano chiaro:

Velocità pin: 8 Gbps;

Interfaccia: 2.048 bit;

Larghezza di banda: ~2 TB/s per stack;

Stack: 12–16 die;

Capacità per package: 36–48 GB;

Consumo stimato: 75 W.

Tra i primi dispositivi a integrarla ci saranno le NVIDIA Rubin (con la versione Ultra che raddoppierà gli stack da 8 a 16) e le AMD Instinct MI500, che potrebbero raggiungere 432 GB di HBM per singolo acceleratore.

HBM5 (2029): doppia interfaccia, doppia banda

Nel 2029, HBM5 manterrà la velocità per pin a 8 Gbps, ma raddoppierà il numero di linee dati:

Interfaccia: 4.096 bit;

Larghezza di banda: 4 TB/s per stack;

Stack: 16 die da 40 Gb;

Capacità per stack: fino a 80 GB;

Consumo stimato: 100 W.

NVIDIA introdurrà probabilmente Feynman, un acceleratore dotato di 400–500 GB di HBM5 in un pacchetto multi‑die, con consumi sopra i 4.400 W totali.

HBM6 (2032): verso i 16 Gbps e 8 TB/s

Con HBM6, previsto per il 2032, si compie un nuovo balzo tecnologico:

Velocità pin: 16 Gbps;

Interfaccia: 4.096 bit;

Banda per stack: 8 TB/s;

Stack: fino a 20 layer;

Capacità per stack: 120 GB;

Potenza: 120 W.

Tecnologie come il raffreddamento a immersione e il bonding rame-rame senza bump diventeranno standard per gestire il calore crescente.

HBM7 (2035): 24 Gbps e 24 TB/s, si entra nel futuro estremo

Il 2035 vedrà l’arrivo di HBM7, un vero colosso della memoria:

Velocità pin: 24 Gbps;

Interfaccia: 8.192 bit;

Larghezza di banda: 24 TB/s per stack;

Capacità: 192 GB per stack;

Potenza: 160 W.

Per gestirla, NVIDIA starebbe progettando un acceleratore da 15.360 W, una cifra finora inimmaginabile.

HBM8 (2038): 64 TB/s e oltre 200 GB per stack

L’ultima tappa nota del percorso, HBM8, è prevista per il 2038:

Velocità pin: 32 Gbps;

Interfaccia: 16.384 bit;

Banda per stack: 64 TB/s;

Capacità: 200–240 GB;

Potenza: 180 W;

Raffreddamento integrato direttamente nel package.

Verso l’integrazione con HBF: memoria flash ad alta banda

Oltre alla DRAM pura, il briefing ha anticipato anche una nuova architettura ibrida HBM-HBF (High-Bandwidth Flash), che combina stack di DRAM con moduli NAND flash attraverso TSV (Through Silicon Via) ad alta velocità. Questa soluzione ibrida punta a coprire le crescenti esigenze della inferenza AI su larga scala, dove petabyte/s di larghezza di banda e architetture multi‑chiplet saranno lo standard.

Conclusione: HBM, il futuro imprescindibile degli acceleratori

Il percorso tracciato da KAIST e TERA è chiaro: l’evoluzione degli acceleratori AI non può prescindere da una memoria che cresca di pari passo in banda, densità e efficienza energetica. Dall’HBM4 in arrivo tra un anno fino all’HBM8 nel 2038, il futuro della computazione ad alte prestazioni passa per queste soluzioni verticali, compatte e straordinariamente veloci. Un panorama che promette non solo potenza, ma anche una trasformazione profonda nell’architettura dei sistemi.

HW Legend Staff