Grazie all’analisi dettagliata di Chips and Cheese, stiamo scoprendo che i nuovi processori Ryzen AI di AMD per laptop, con nome in codice “Strix Halo“, utilizzano un sistema di interconnessione parallelo a “mare di fili” tra i chiplet, sostituendo l’approccio SERDES (serializer/deserializer) trovato nei modelli Ryzen desktop.

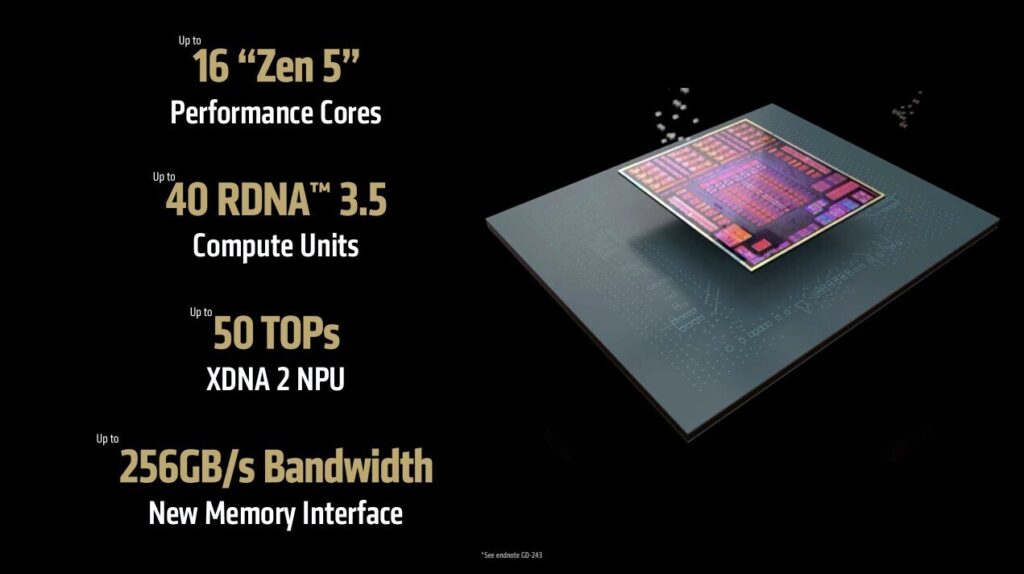

L’implementazione fisica del processore consiste di due Core Complex Dies (CCD), ciascuno prodotto con il processo N4 (4 nm) di TSMC e contenente fino a otto core Zen 5 con unità a virgola mobile a 512 bit. In modo interessante, anche il die I/O (IOD) è realizzato con il processo N4, segnando un progresso rispetto al processo N6 (6 nm) utilizzato negli IOD standard dei Ryzen desktop.

Il cambiamento principale risiede nel sistema di comunicazione tra chiplet: mentre la serie Ryzen 9000 (Granite Ridge) utilizza SERDES per convertire i dati paralleli in seriali per la trasmissione tra i chiplet, Strix Halo implementa una trasmissione diretta dei dati paralleli tramite connessioni fisiche multiple.

Questo design consente un throughput di 32 byte per ciclo di clock e elimina il sovraccarico di latenza associato ai processi di serializzazione/deserializzazione. L’architettura di interconnessione parallela elimina anche la necessità di riqualificare le connessioni durante le transizioni di stato di alimentazione, una limitazione presente nelle implementazioni SERDES.

Tuttavia, questa scelta progettuale richiede una maggiore complessità del substrato a causa della maggiore densità delle connessioni e richiede più pin per le connessioni esterne, suggerendo possibili modifiche al design del CCD rispetto alle varianti desktop. L’implementazione di AMD ha richiesto processi di fabbricazione del substrato più complessi per accomodare le connessioni parallele dense tra i chiplet.

La decisione di privilegiare questo approccio progettuale più complesso è stata dettata dalla necessità di ridurre la latenza e il consumo energetico nei carichi di lavoro ad alta intensità di dati, dove una comunicazione ad alta larghezza di banda e consistente tra i chiplet è cruciale.

HW Legend Staff