AMD sta preparando due importanti processori per segmenti di client basati sulla nuova microarchitettura “Zen 6“, secondo un sensazionale report di Moore’s Law is Dead. Si tratta del processore mobile “Medusa Point” e del desktop “Olympic Ridge”. Il primo è un BGA simile in dimensioni e Z-Height all’attuale “Strix Point”, mentre il secondo è progettato per il socket AM5 esistente, rendendolo la terza (e probabilmente ultima) microarchitettura a supportarlo. Se ricordi, il socket AM4 ha servito tre generazioni di Zen, senza contare il refresh “Zen+”. Al centro dell’iniziativa c’è un nuovo die del complesso CPU (CCD) che AMD intende usare per tutta la sua linea di client e server.

Il “Zen 6” performance CCD è progettato per un nodo da 3 nm, probabilmente il TSMC N3E. Questo nodo promette un significativo aumento della densità dei transistor, miglioramenti in termini di potenza e velocità di clock rispetto all’attuale nodo TSMC N4P utilizzato per il “Zen 5” CCD. Qui le cose diventano interessanti. Il CCD contiene dodici core “Zen 6” completi, segnando il primo aumento nel numero di core delle CPU di prestazioni di AMD dal suo primo “Zen” CCD. Tutti e 12 questi core fanno parte di un unico complesso di core CPU (CCX) e condividono una cache L3 comune. Potrebbe esserci un aumento proporzionale della dimensione della cache fino a 48 MB. Si prevede anche che AMD migliori il modo in cui i CCD comunicano con il die I/O e tra di loro.

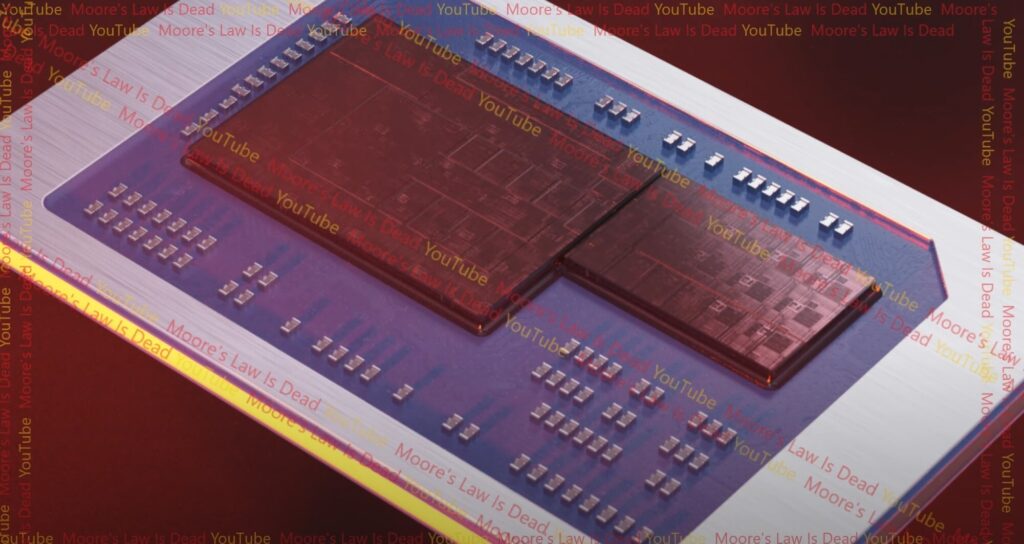

Tornando alla serie Ryzen 3000 “Matisse”, i due CCD dei processori desktop client avevano link Infinity Fabric verso il die I/O, ma senza connessioni dirette ad alta larghezza di banda tra i due CCD. Per fare in modo che i thread migrassero tra i core dei due CCD, dovevano fare un viaggio di andata e ritorno attraverso la memoria principale. AMD sta cercando di risolvere questo problema con l’introduzione di una nuova connessione a bassa latenza tra i due CCD. Se l’obiettivo è consentire ai thread di migrare senza soluzione di continuità tra i core dei due CCD, eliminando i viaggi nella memoria principale, lo scopo di questa connessione è stabilire la coerenza della cache tra i due CCD. Questo ridurrebbe enormemente la latenza intercore.

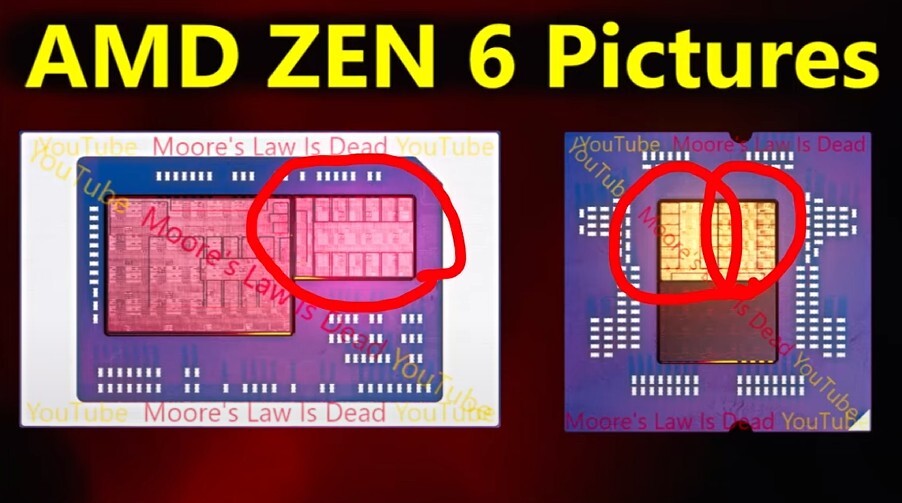

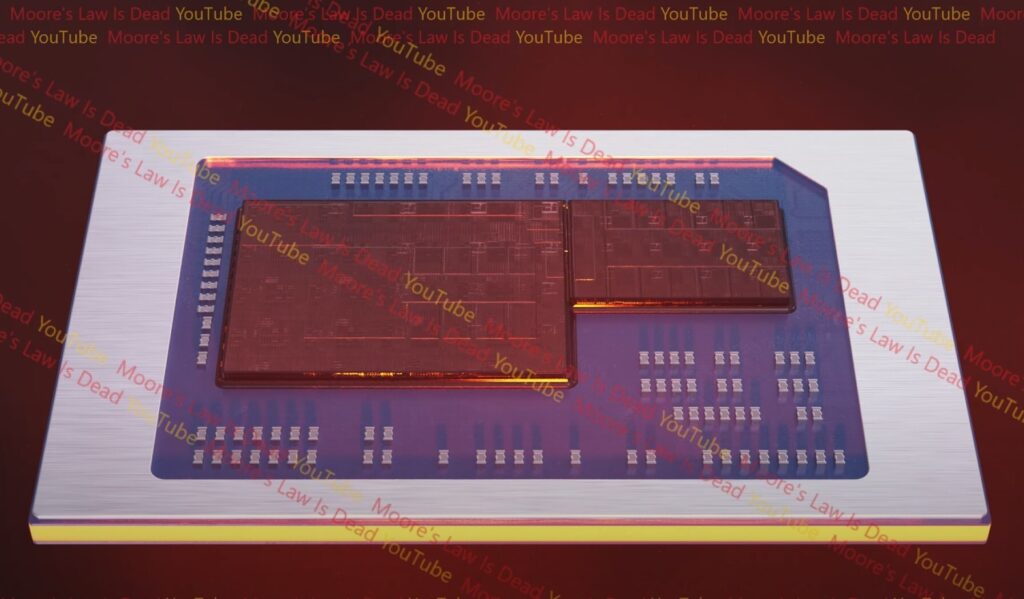

Ecco dove le cose diventano davvero interessanti. Apparentemente, il processore mobile “Medusa Point” è basato su chiplet, e utilizzerà un chiplet “Zen 6” a 12 core, con un grande die I/O mobile client costruito su un nodo precedente, probabilmente il N4P. Questo I/O mobile cIOD conterrà una iGPU aggiornata alimentata dalla nuova architettura grafica RDNA 4. Conterrà anche i controller di memoria del chip e un NPU aggiornato. Speriamo che AMD lavori per aumentare il numero di linee PCIe offerte da questo I/O die, o almeno aggiornarlo a PCIe Gen 5. Le immagini mostrano piccole strutture rettangolari sul mobile client I/O die, suscitando alcune speculazioni sul fatto che potrebbe trattarsi di un CCX a bassa potenza con core “Zen 6c”, anche se MLID smentisce questa ipotesi, affermando che si tratta di workgroup processors (WGPs) della iGPU. Ce ne sono otto e una grande porzione di cache L2, il che sembra confermare che la iGPU è basata sull’architettura grafica RDNA 4 e abbia 16 unità di calcolo (CU).

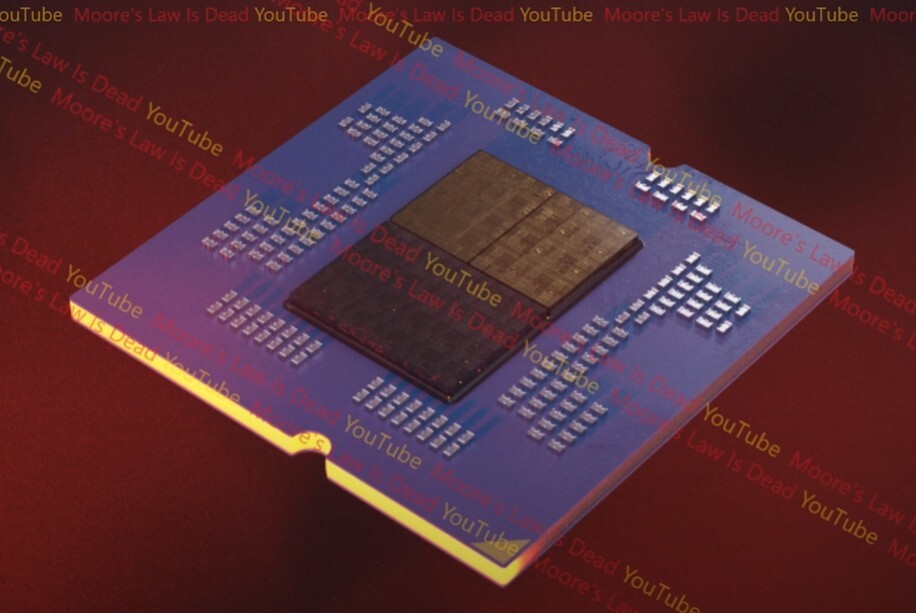

Poiché AMD utilizza lo stesso CCD per “Medusa Point” come per il processore desktop “Olympic Ridge”, ci si può aspettare varianti di “Medusa Point” con 3D V-Cache. Si prevede che la tecnologia 3D V-Cache venga implementata su “Zen 6” nello stesso modo in cui è stata implementata su “Zen 5”, con uno stacking rovesciato: il die 3D V-Cache (L3D) sotto, con il CCD sopra. Dato l’aumento nel numero di core della CPU, soprattutto con “Olympic Ridge” che arriverà fino a 24 core con due CCD, e la connessione inter-CCD per la coerenza della cache, AMD avrà bisogno di un nuovo cIOD per il desktop.

Si prevede che il nuovo cIOD venga costruito sul nodo di fonderia Samsung 4LPP (4 nm EUV), che offre miglioramenti rispetto al nodo TSMC N6 DUV su cui è attualmente costruito l’attuale cIOD. Un’area chiave di focus per AMD saranno i controller di memoria, che saranno aggiornati per supportare velocità di memoria DDR5 più elevate utilizzando tecnologie come CKD. Attualmente, è possibile eseguire un processore “Granite Ridge” con velocità di memoria fino a DDR5-8000, ma utilizzando un divisore di clock 1:2 tra FCLK e MCLK, con velocità 1:1 limitate a circa DDR5-6400. I nuovi controller di memoria cercheranno di aumentare le velocità con 1:1, e sbloccare velocità oltre i 10000 MT/s con 1:2.

Poi c’è la questione dell’accelerazione AI, e il nuovo cIOD offrirà ad AMD l’opportunità di implementare almeno un NPU XDNA 2 da 50 TOPS. Intel è stata criticata per aver dato ai suoi processori “Arrow Lake” un NPU da 16 TOPS che non soddisfa i requisiti Copilot+, e l’azienda probabilmente sta lavorando per risolvere questo problema in “Panther Lake”. Se AMD decidesse di implementare un NPU sul cIOD per “Olympic Ridge”, prevediamo che sarà almeno della classe 50 TOPS.

HW Legend Staff