AMD “Granite Ridge” è il nome in codice dei quattro nuovi processori desktop della serie Ryzen 9000 che l’azienda prevedeva di lanciare il 31 luglio 2024. Oggi sappiamo che l’arrivo sul mercato di tali CPU è stato ritardato.

I processori sono basati sul package Socket AM5 e dovrebbero essere retrocompatibili con le schede madri con chipset AMD serie 600, oltre a quelle con chipset serie 800 che verranno lanciate insieme a tali CPU.

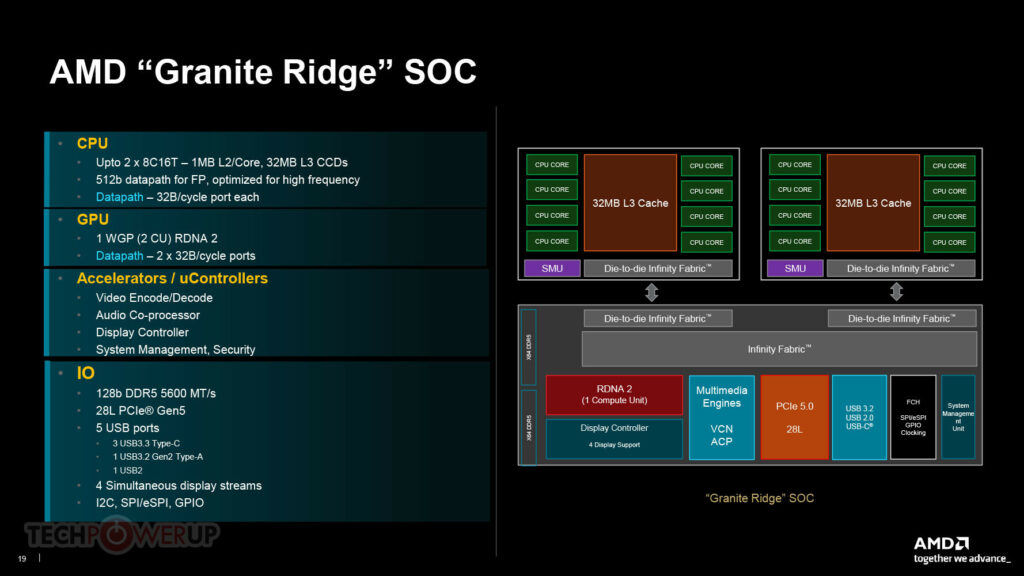

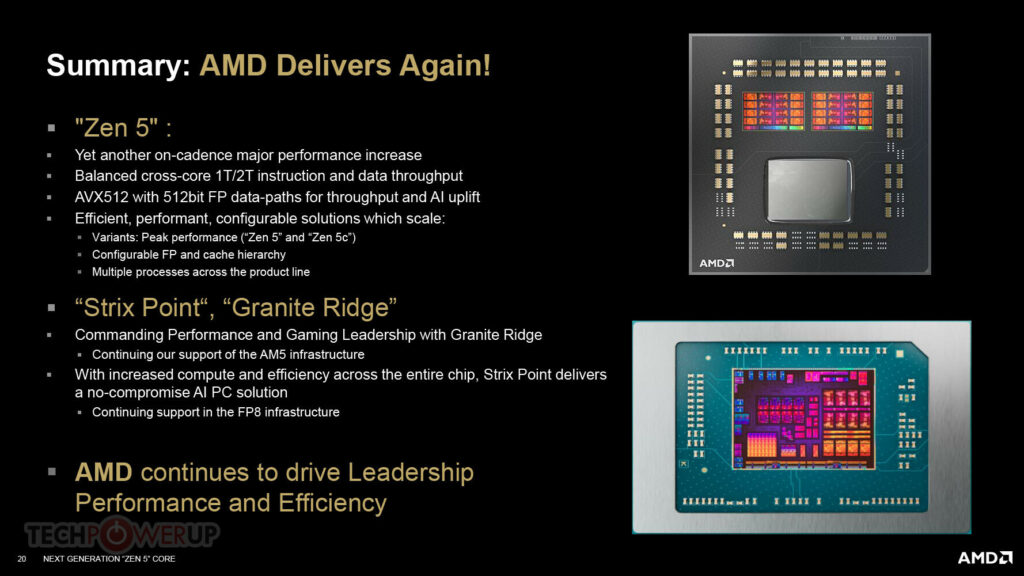

“Granite Ridge” è un processore basato su chiplet, molto simile a Ryzen 7000 “Raphael”, Ryzen 5000 “Vermeer” e Ryzen 3000 “Matisse”. AMD sta trasferendo il die I/O client a 6 nm da “Raphael” nel tentativo di ridurre al minimo i costi di sviluppo, più o meno nello stesso modo in cui ha trasferito il cIOD a 12 nm da “Vermeer” a “Matisse”.

Le funzionalità I/O SoC di “Granite Ridge” sono moderne grazie all’adozione del PCI-Express Gen 5 a 28 corsie che consente un PCI-Express 5.0 x16, due slot M.2 Gen 5 collegati alla CPU e un bus chipset Gen 5 x4. C’è anche una soluzione grafica integrata di base basata sulla vecchia architettura grafica RDNA 2; che dovrebbe rendere questi processori adatti a tutti i casi d’uso che non necessitano di grafica discreta.

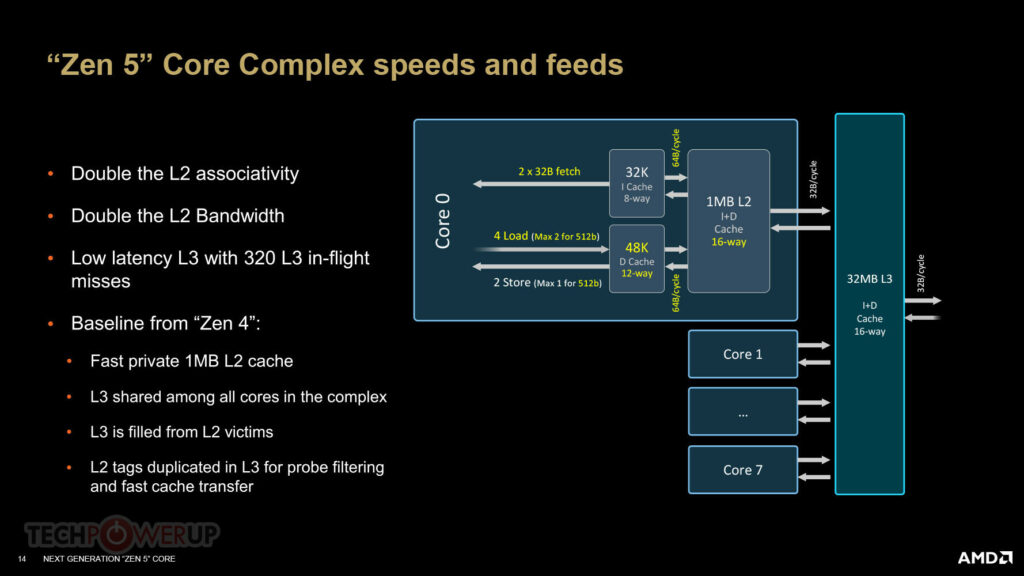

L’iGPU ha persino acceleratori multimediali, un coprocessore audio, un controller di visualizzazione e interfacce USB 3.2 dal processore. Passando ai die complessi CPU (CCD), che sono al centro dell’innovazione di AMD, l’azienda ha confermato che i CCD “Zen 5” a 8 core, internamente denominati “Eldora”, sono costruiti sul nodo della fonderia TSMC N4P.

Rispetto al nodo N5 su cui è costruito il CCD “Zen 4”, il nodo N4P offre una massiccia riduzione di potenza del 22% a livello di nodo, un miglioramento delle prestazioni del 6% e un miglioramento del 6% nella densità dei transistor. La produzione di massa di “Eldora” sarebbe iniziata verso l’inizio-metà del primo semestre del 2024, quando N4X non sarebbe stato ancora pronto per la produzione di massa.

Ognuno dei due CCD comunica con il cIOD tramite IFoP (Infinity Fabric over Package), con le stesse letture da 32 B/ciclo per porta e scritture da 16 B/ciclo per porta. Ogni CCD ha otto core CPU “Zen 5” full-size, con i loro percorsi dati FP da 512 bit completamente disponibili. Ognuno degli otto core ha una cache L2 dedicata da 1 MB e gli otto condividono una cache L3 da 32 MB. Gli unici altri componenti del CCD sono l’interfaccia IFoP e una SMU.

HW Legend Staff

![Kingston FURY Renegade G5 NVMe M.2 SSD 2TB [SFYR2S/2T0] Cop - Kingston FURY Renegade G5 NVMe M.2 SSD 2TB [SFYR2S2T0]](https://www.hwlegend.tech/wp-content/uploads/2025/10/Cop-Kingston-FURY-Renegade-G5-NVMe-M.2-SSD-2TB-SFYR2S2T0-150x150.webp)