AMD, nella sua sessione di domande e risposte approfondita sull’architettura con la stampa, ha confermato che i core “Zen 5” e “Zen 5c” sul silicio “Strix Point”, presentano solo percorsi dati FPU di 256 bit di larghezza, a differenza dello “Zen 5” core presenti nei processori desktop “Granite Ridge” Ryzen 9000.

“Lo Zen 5c utilizzato in Strix ha un percorso dati a 256 bit, così come lo Zen 5 utilizzato all’interno di Strix”, ha affermato Mike Clark, membro aziendale di AMD e capo dell’architettura dei core della CPU “Zen”.

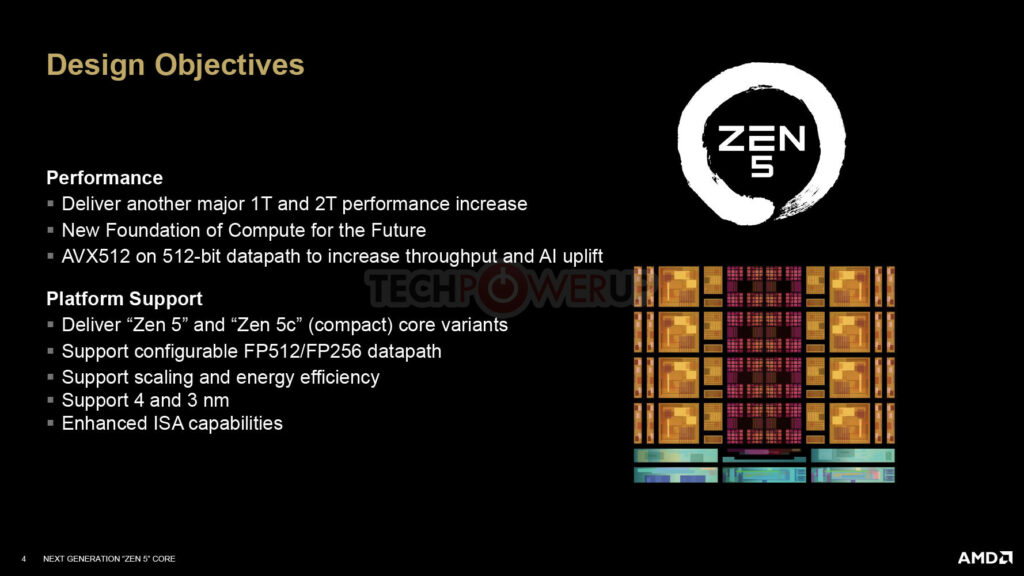

A quanto pare, AMD ha sviluppato una variante dei core “Zen 5” e “Zen 5c” che mancano fisicamente dei percorsi dati a 512 bit. Ciò suggerisce che i core “Zen 5” e “Zen 5c” su “Strix Point” sono fisicamente più piccoli di quelli sul CCD a 8 core “Eldora” da 4 nm presente in “Granite Ridge” e in alcuni dei modelli chiave dei prossimi processori server EPYC “Torino” di quinta generazione.

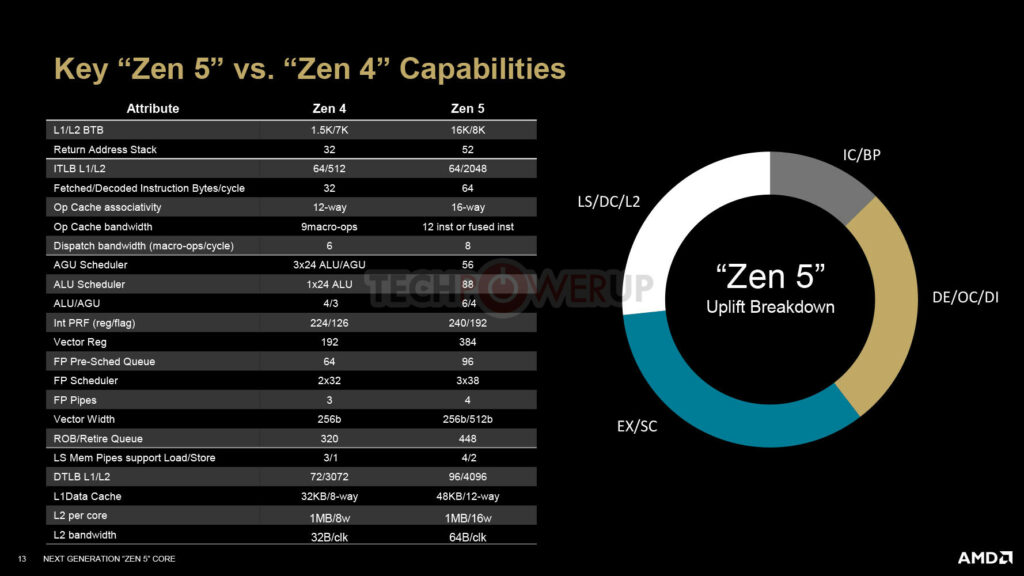

Una delle attrazioni principali della microarchitettura “Zen 5” è la sua unità a virgola mobile, che supporta AVX512 con un percorso dati completo a 512 bit. In confronto, la generazione precedente “Zen 4” gestiva AVX512 utilizzando una FPU a doppio canale a 256 bit. La nuova FPU a 512 bit, a seconda del carico di lavoro e di altri fattori, è circa il 20-40% più veloce di “Zen 4”, nei carichi di lavoro in virgola mobile a 512 bit, motivo per cui si prevede che “Zen 5” registrerà miglioramenti significativi nelle prestazioni riguardanti l’intelligenza artificiale.

Non siamo sicuri di come la mancanza di un percorso dati FP a 512 bit influenzi le prestazioni delle istruzioni relative all’accelerazione AI, poiché “Strix Point” è progettato principalmente per PC AI predisposti per Microsoft Copilot+. È possibile che AVX512 e AVX-VNNI vengano eseguiti su un percorso dati a 256 bit a doppio canale simile a come viene eseguito su “Zen 4”. Potrebbero esserci alcuni vantaggi in termini di prestazioni/Watt nel farlo in questo modo, risultano decisamente validi specialmente nelle piattaforme mobili.

HW Legend Staff