AMD ha recentemente depositato un brevetto che svela piani per implementare il “multi-chip stacking” nei futuri SoC Ryzen, secondo un rapporto di Wccftech citato da un post su X di @coreteks.

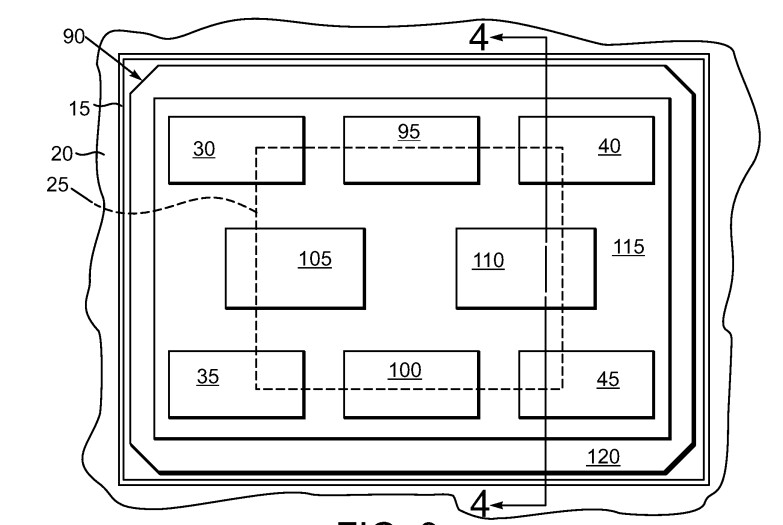

Il brevetto descrive un design innovativo che consente l’impilamento compatto e l’interconnessione di chip attraverso un layout in cui chiplet più piccoli si sovrappongono parzialmente a un die più grande. La linea tratteggiata rappresenta un die più grande sovrapposto a chiplet più piccoli.

Questa tecnologia mira a ottimizzare l’area di contatto tra i componenti, consentendo core count più elevati, cache più ampie e maggiore larghezza di banda di memoria senza aumentare la dimensione del die.

Il design riduce anche la distanza fisica tra i componenti, minimizzando la latenza di interconnessione e migliorando la comunicazione tra le diverse parti del chip. Inoltre, l’approccio migliora la gestione dell’alimentazione, poiché i chiplet separati consentono un controllo più preciso attraverso il power gating.

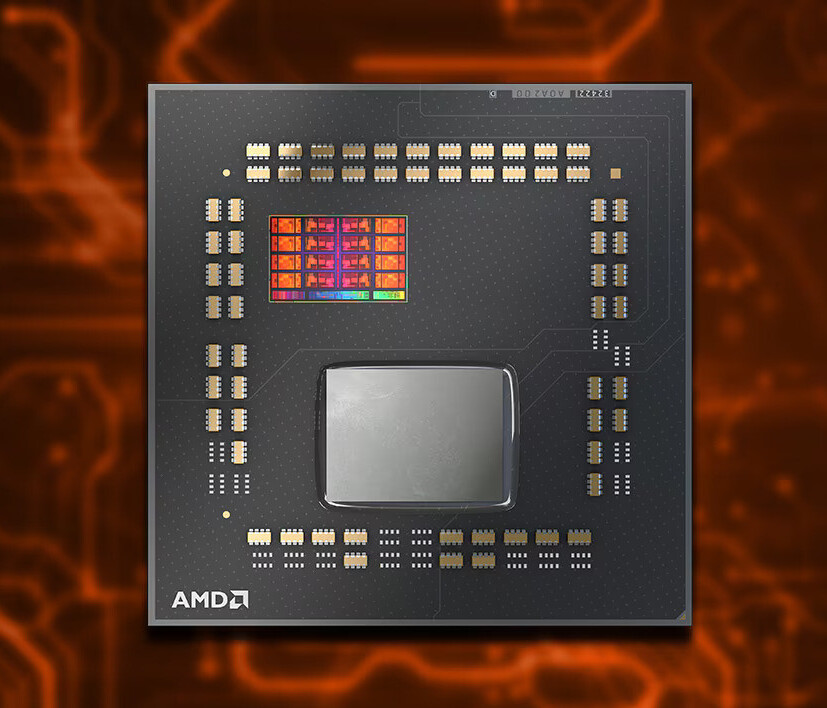

AMD sembra impegnata a superare l’architettura monolitica, puntando su chiplet multipli. Questo approccio, simile a quanto avvenuto con la tecnologia 3D V-Cache che ha reso la linea di processori X3D un successo, potrebbe avere un ruolo cruciale nei futuri SoC Ryzen. Tuttavia, il passaggio dal brevetto alla produzione e al prodotto finale potrebbe richiedere del tempo, restando per ora una prospettiva futura.

HW Legend Staff